介绍 #

Placement #

良好的布局会带来更好的芯片面积利用率、时序性能和可达性,而较差的布局会影响芯片的性能,甚至使其无法制造

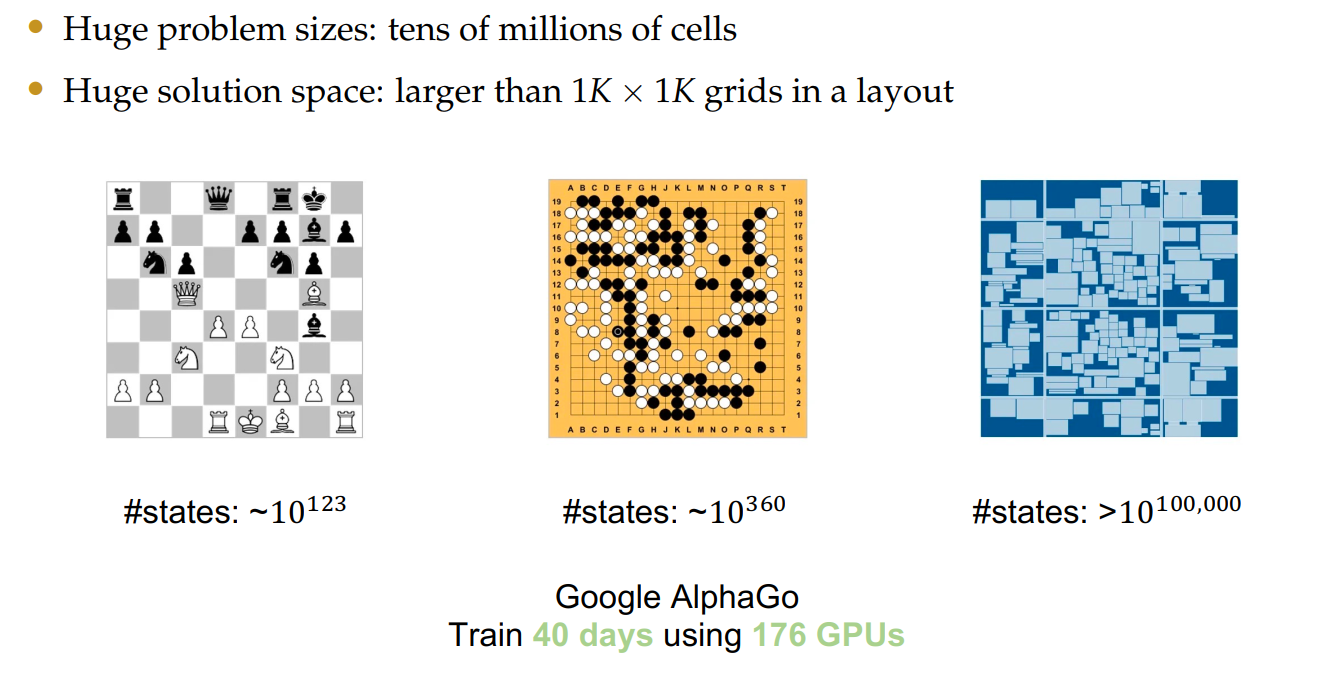

布局可以看作是具有几何约束的二维装箱问题的一个更为复杂的变化。后者被认为是 NP-hard 问题。

布局与电路设计的逻辑互连和逻辑元件的几何位置有关。由于在布线之前无法准确评估放置解决方案的质量,导致设计流程中的反馈循环很长,因此现代布局需要在早期阶段减少布线拥塞(Congestion)并提高可达性(Routebility)

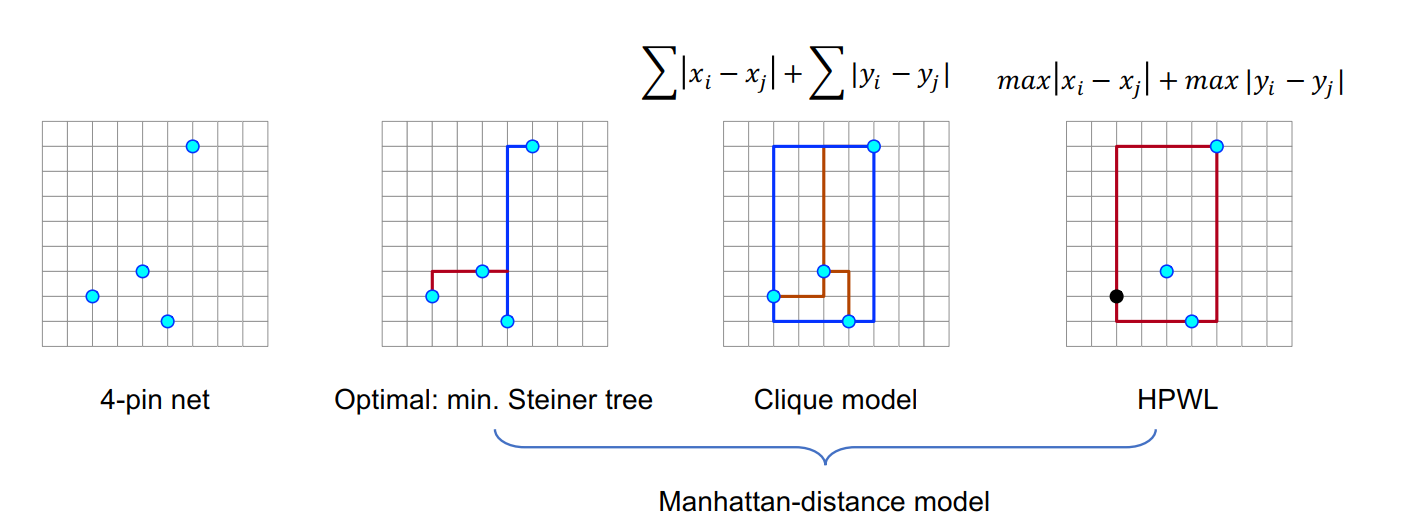

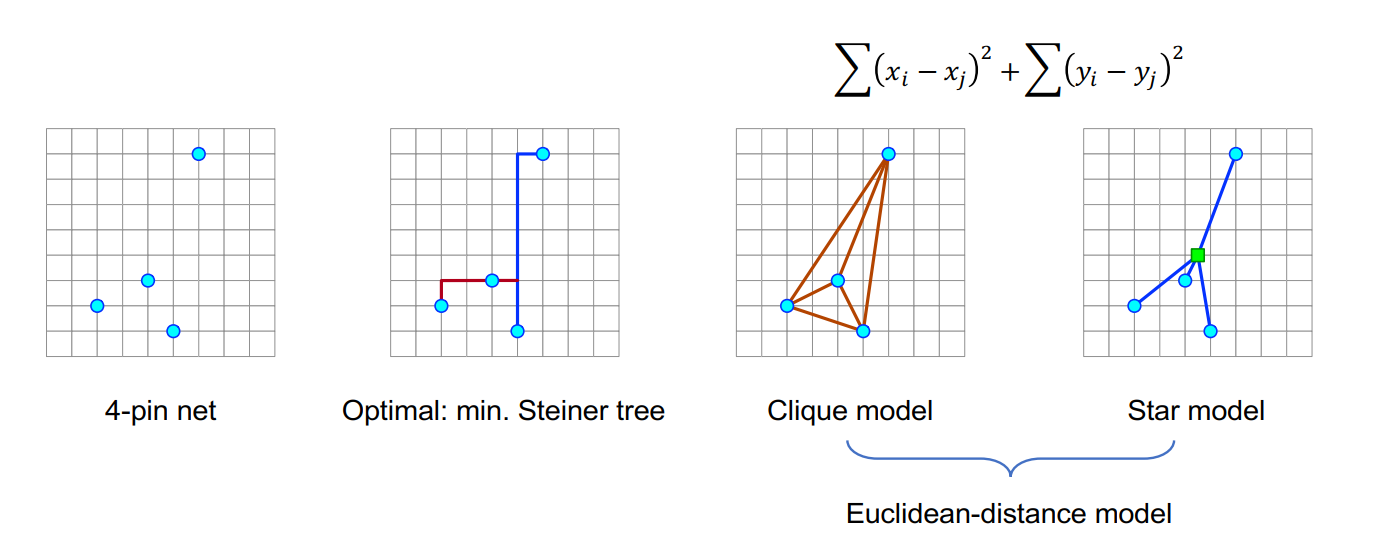

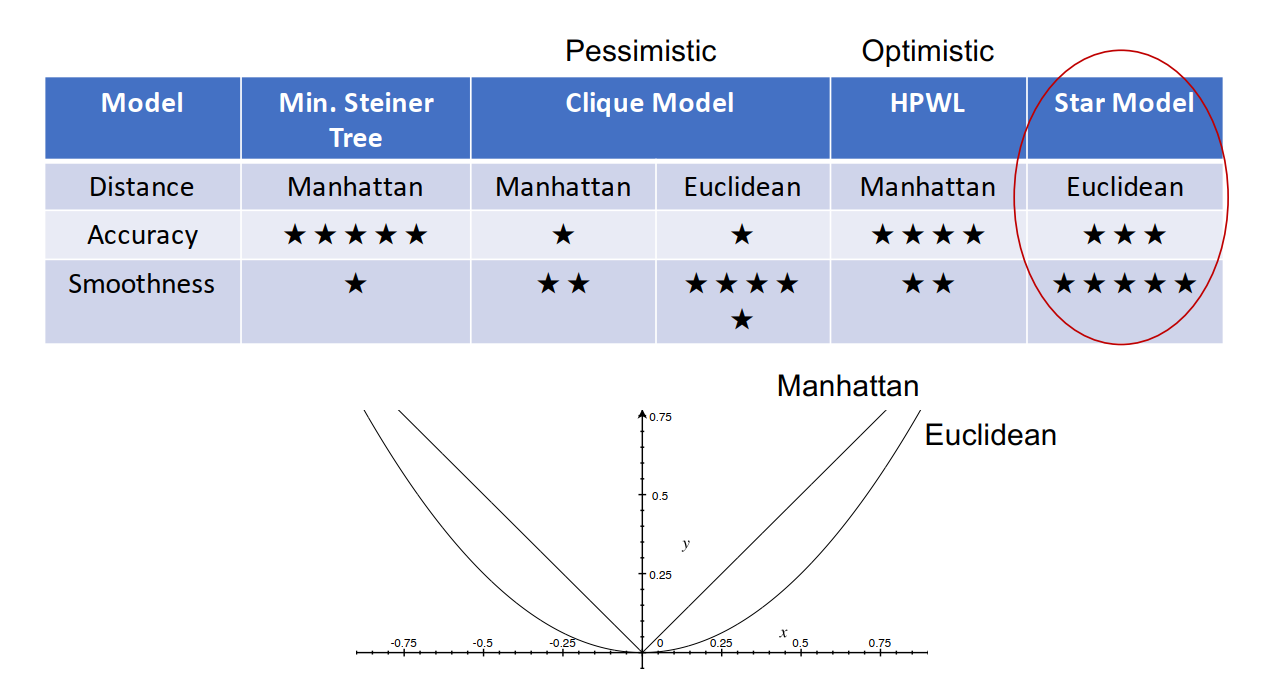

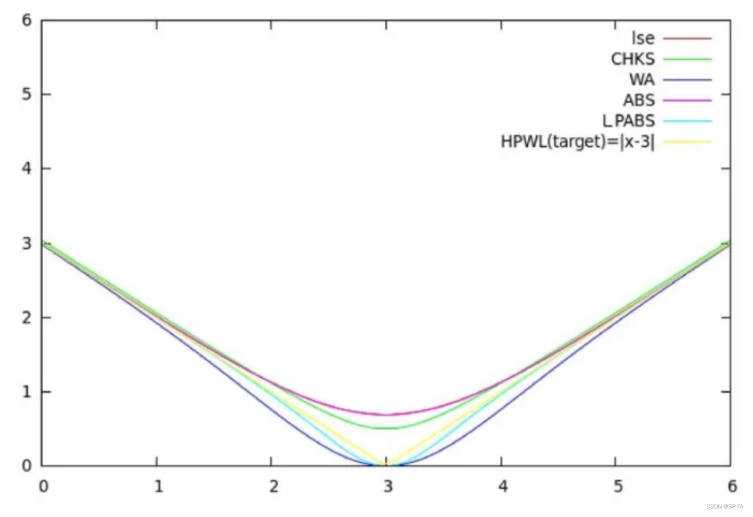

WL估计方法 #

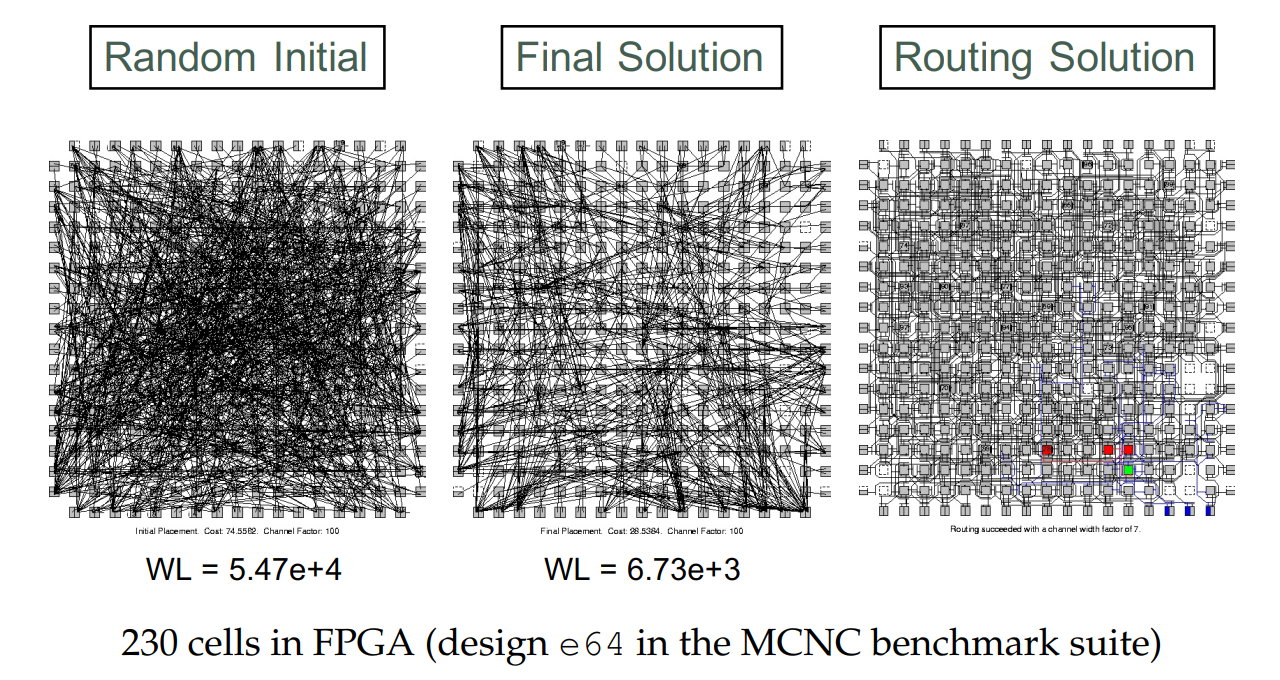

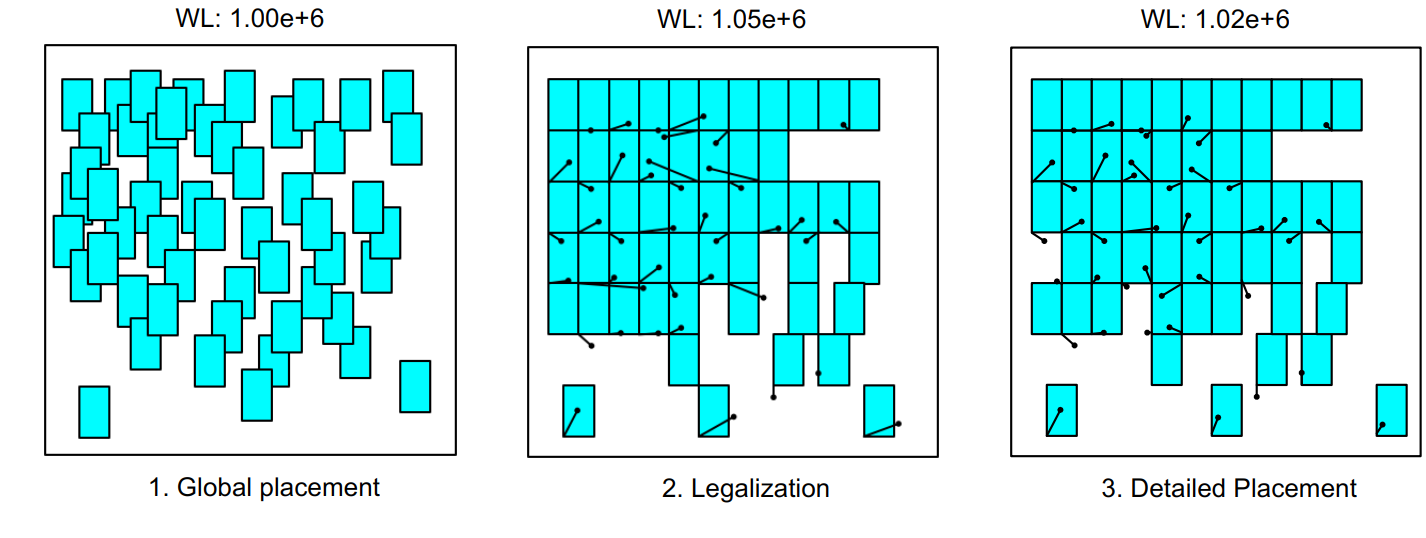

Global Placement #

通常,全局布局(Global Placement)涉及宏布局(Macro Placement)和标准单元布局(Standard Cell Placement)。

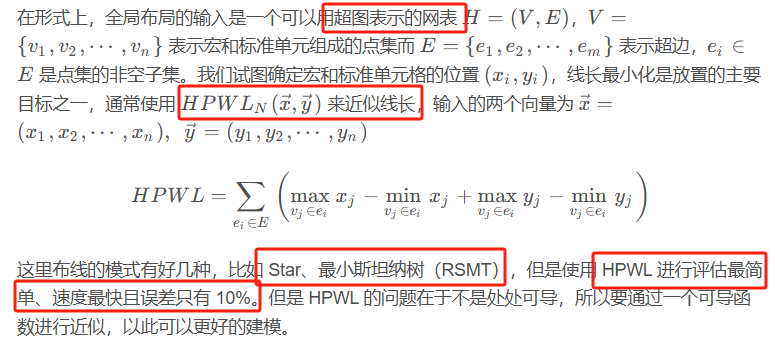

输入:网表

优化目标:HPWL线长最小(最基本)…

Detail Placement #

详细布局(Detailed Placement)包括合法化(legalization),线长(wirelength)和可达性的细化(routability refinement)

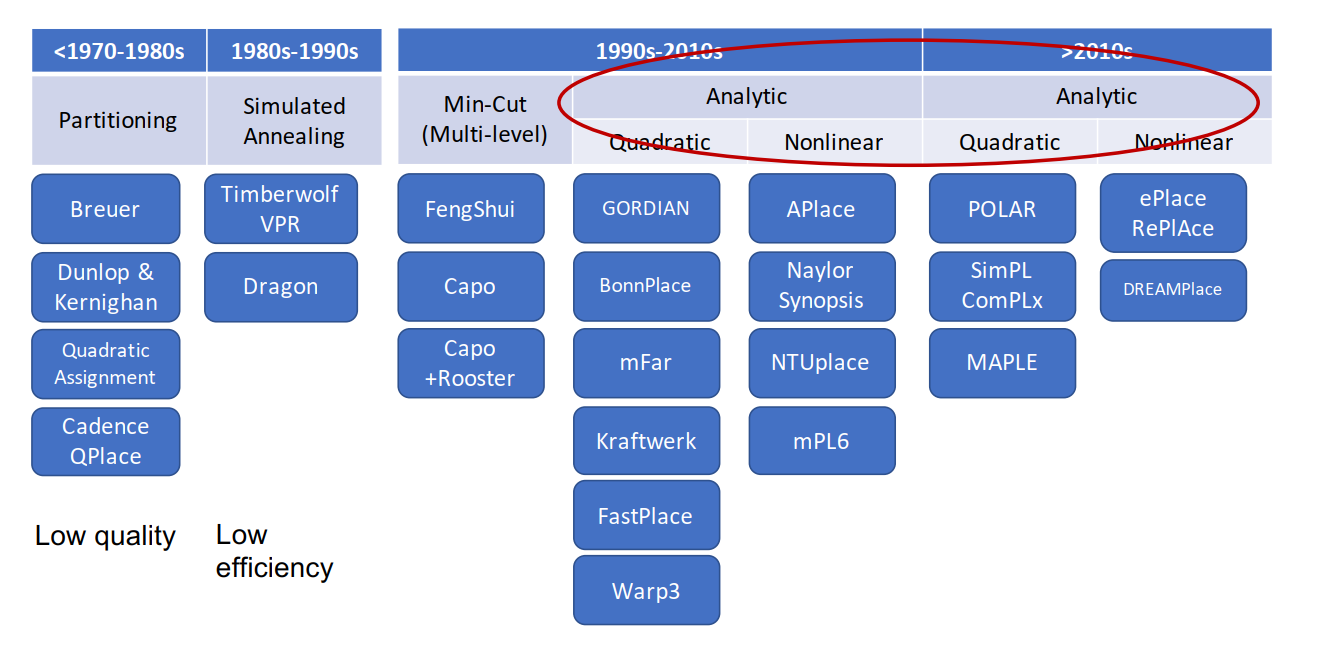

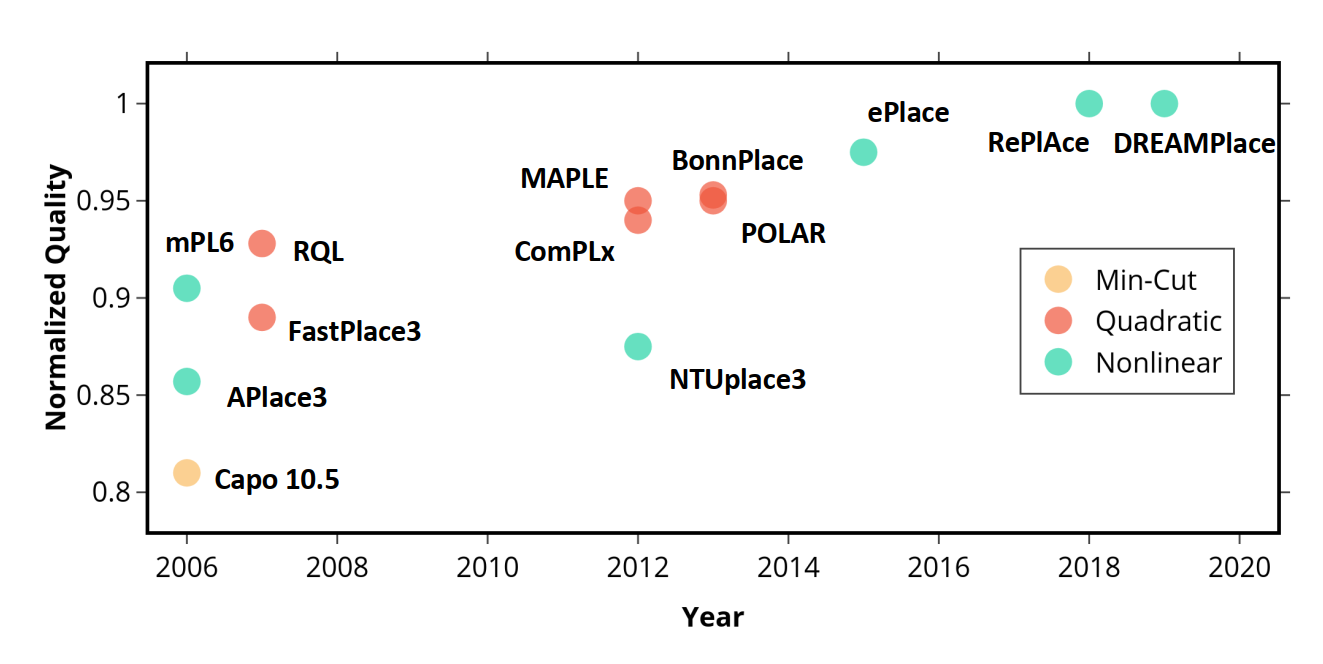

history #